Halbleiterfertigung: TSMCs N2-Prozess nutzt Nanosheets

15 Prozent schneller oder 30 Prozent sparsamer: Auch TSMC setzt künftig auf GAA-Transistoren. Zudem gibt es konfigurierbare 3-nm-Verfahren.

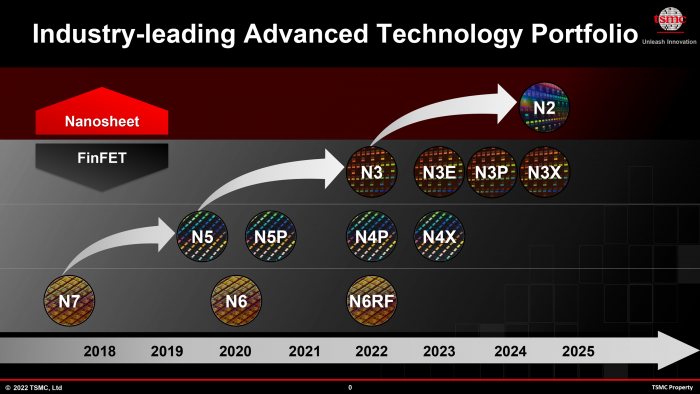

TSMC hat die N2-Fertigung angekündigt: So heißt verkürzt der neue Fertigungsprozess, der ab dem zweiten Halbjahr 2025 einsatzbereit sein soll und EUV-Belichtung mit GAA-Transistoren auf Basis von Nanosheets vereint. Davor sind mit N3E, N3P und N3X gleich drei 3-nm-Verfahren mit klassischen Finfets sowie variablen Finflex-Zellen geplant.

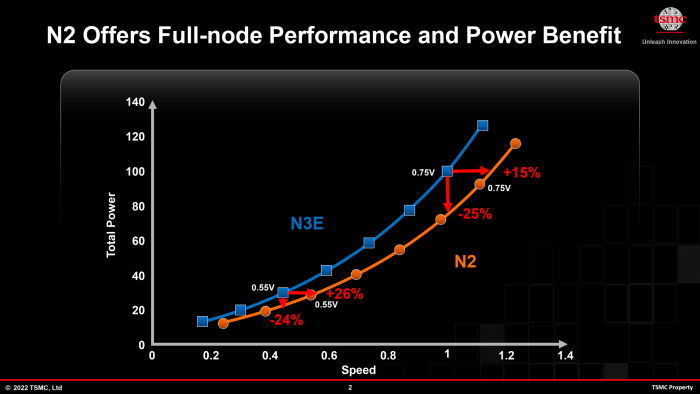

Verglichen mit der N3(E)-Fertigung soll N2 eine 10 bis 15 Prozent höhere Performance bei identischer Leistungsaufnahme erreichen oder aber bei gleicher Geschwindigkeit zwischen 25 und 30 Prozent sparsamer sein. Die Transistordichte steigt um 10 Prozent, wobei TSMC sich hier auf eine 50/30/20-Mischung aus Logik, SRAM und Analog bezieht.

Nanosheets für GAA

N2 ist der erste Node des Auftragsfertigers, der Gate-All-Around-Transistoren (GAA) nutzt. Hierbei wird der Kanal vollständig vom schaltenden Gate umgeben, wobei die Transistoren auf Nanosheets statt Finfets basieren. Sie sind überdies anpassbar, weshalb TSMC von N2 eine Mobile- und eine High-Performance-Variante anbieten will.

| Geschwindigkeit | Leistungsaufnahme | Dichte | |

|---|---|---|---|

| N5 vs N7 | plus 15 % | minus 30 % | 1,80x |

| N5P vs N7 | plus 20 % | minus 40 % | 1,80x |

| N5P vs N5 | plus 5 % | minus 10 % | (?) |

| N4 vs N5 | (?) | (?) | 1,06x |

| N4P vs N5 | plus 11 % | minus 22 % | 1,06x |

| N4X vs N5 | plus 15 % | minus 21 % | 1,06x |

| N4X vs N4 | plus 6 % | (?) | (?) |

| N3B vs N5 | plus 10 - 15 % | minus 25 - 30 % | 1,60x |

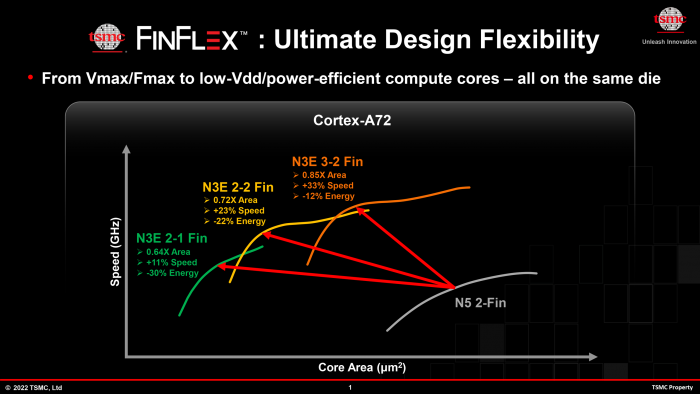

| N3E (2-1) vs N5 (2 Fin) | plus 11 % | minus 30 % | 1,56x |

| N3E (2-2) vs N5 (2 Fin) | plus 23 % | minus 22 % | 1,39x |

| N3E (3-2) vs N5 (2 Fin) | plus 33 % | minus 12 % | 1,18x |

| N2 vs N3E | plus 10 - 15 % | minus 25 - 30 % | 1,10x |

Für die 3-nm-Generation sind ebenfalls unterschiedliche Ableger geplant: N3E statt N3 soll verglichen mit N5 die Performance um bis zu 34 statt 25 bis 30 Prozent verbessern oder aber die Leistungsaufnahme um bis zu 18 statt 10 bis 15 Prozent reduzieren. Die Dichte steigt allerdings nur um 60 statt 70 Prozent, ein zu erwartender Kompromiss. N3 soll im zweiten Halbjahr 2022 in Serie gehen, N3E im zweiten Halbjahr 2023.

Auf N3E folgt mit N3P eine noch mehr auf Performance optimierte Stufe und mit N3X wird dieses Ausrichtung erneut verstärkt. Wie sich diese beiden Nodes verglichen mit N3(E) schlagen, sagte TSMC nicht. Dafür erläuterte der Auftragsfertiger die variablen Finflex-Zellen, mit denen sich N3E optimieren lässt.

Heutige Chips können zwar High-Performance- und High-Density-Bibliotheken mischen, allerdings begrenzt auf ganze Blöcke wie CPU-Kerne statt auf den zugrunde liegenden Zellen. Per Finflex lassen sich Letztere mit Blick auf die P- und N-Fins der darin zusammengefassten Transistoren konfigurieren: 3-2 liefert die höchste Geschwindigkeit bei geringer Dichte sowie mäßiger Effizienz, 2-2 ist ein Mittelweg und 2-1 soll besonders effizient sowie dicht bei niedrigen Leckströmen sein.

Zwischen N3 und N5(P) gibt es noch N4(P) sowie N4X, womit TSMC nahezu in Prozentschritten gestaffelte Verfahren anbietet.

Ja, ich bin auch gespannt. Meine Vermutung wäre, daß das 3D-stacking, das es teilweise...

Nur das nm nicht mehr viel aussagen, es kommt inzwischen auf alles mögliche an. Daher hei...